An SDPF RISC-V Processor with 55.9% Dhrystone Improvement Using Two-Stage Pseudo-Pipelined Architecture for IoT Applications

Abstract

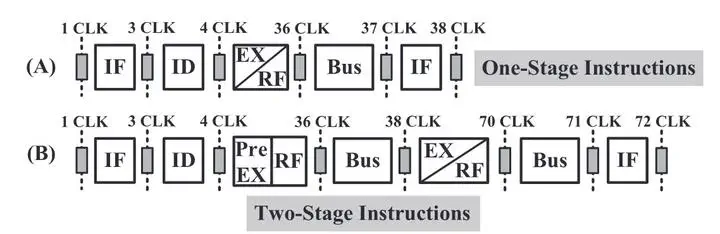

Embedded Internet of Things (IoT) nodes are required to perform lightweight tasks such as information monitoring and simple signal processing. A crucial component of low-power embedded IoT sensors is the low-power processor. Due to the constraints of operating conditions, there are stringent requirements on the power consumption and area of the processor. To minimize the power and area, this paper proposes a low-power RV32I processor based on the RISC-V instruction set architecture (ISA), which adheres to a serial data path. To enhance the energy efficiency of the serial data path followed (SDPF) processor, this paper proposes a pseudo-pipeline architecture. By partitioning and combining certain instruction lifecycle tasks, a two-stage pseudo-pipeline structure is implemented, thereby reducing the cycles per instruction (CPI) of the SDPF processor. The proposed processor is designed using Verilog HDL, and FPGA prototype validation demonstrates that the proposed processor achieves at least 18% fewer resource compared with the traditional parallel 32-bit RISC-V processors and 55.9% performance improvement compared with the previous SDPF processors. The proposed processor is implemented using a standard 0.18-μm CMOS process. The post-layout simulation results indicate that it has at least 9.6% less area and 37.5% lower dynamic power consumption compared with traditional parallel 32-bit processor. Additionally, it achieves a 40.9% increase in the performance to power ratio compared with the previous SDPF RV32I processor.