A Self-Biased Subthreshold CMOS Voltage Reference with Temperature Compensation Circuit for IoT Self-Powered Sensor Applications

Abstract

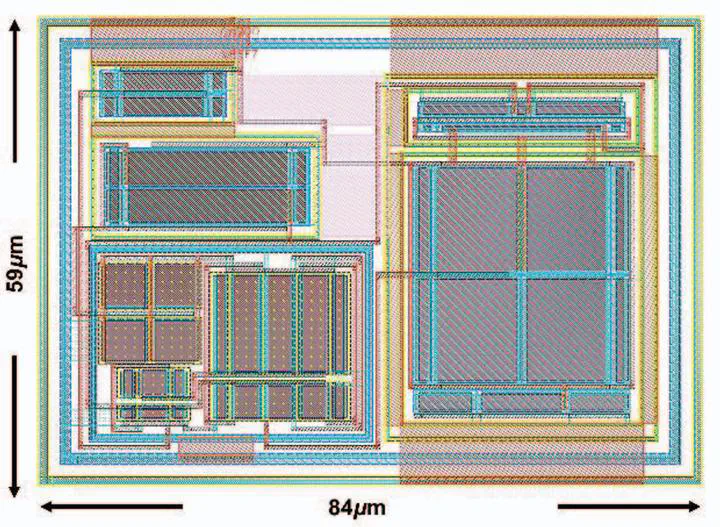

This paper presents a subthreshold CMOS voltage reference structure that utilizes self-biased circuits. This voltage reference includes temperature compensation circuits to expand its operating temperature range and reduce its temperature coefficient. The proposed CMOS voltage reference is designed using a standard 0.18−μm CMOS process and has a small area of only 0.005 mm^2 . Post-layout simulation results demonstrate that the power consumption of the circuit at room temperature (25°C) is only 1.65 nW at a power supply voltage of 1 V. In this case, the voltage reference output is 316.56 mV, with a temperature coefficient (TC) of 2.79 ppm/°C in a wide temperature range from -40°C to 140 °C. Furthermore, the line sensitivity (LS) of the circuit is 0.022 %/V.