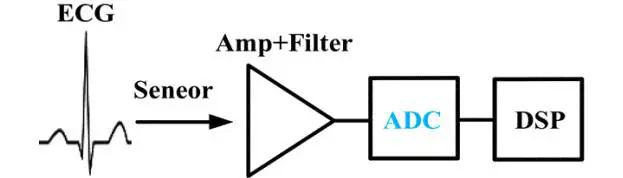

A Second-Order Dual-Charge-Pump Passive Noise-Shaping SAR ADC for Medical Implant Devices

Abstract

A 14.14bit 2MS/s Second-Order Passive Noise-Shaping Successive Approximation Register Analog-to-Digital Converter (NS SAR ADC) is proposed in this paper. The structure utilizes techniques such as charge pumps and multi-input comparator with a gain to compensate for the signal loss during the noise shaping process. It incorporates two zero points at 0.8 in the noise transfer function (NTF), which enhances the noise shaping capability. This ADC is designed using a standard 180nm CMOS process. The simulation results show that the ADC consumes 56.8 μ W, achieving a signal-to-noise-and-distortion ratio (SNDR) of 86.75 dB and a spurious-free dynamic range (SFDR) of 97.16 dB with an oversampling ratio (OSR) of 8 at 2MS/s, resulting in an Schreier figure of merit (FoMs) of 180.18dB.