A 0.6 V 10-bit 20 kHz Capacitor Splitting Bypass Window SAR ADC for Biomedical Applications

Abstract

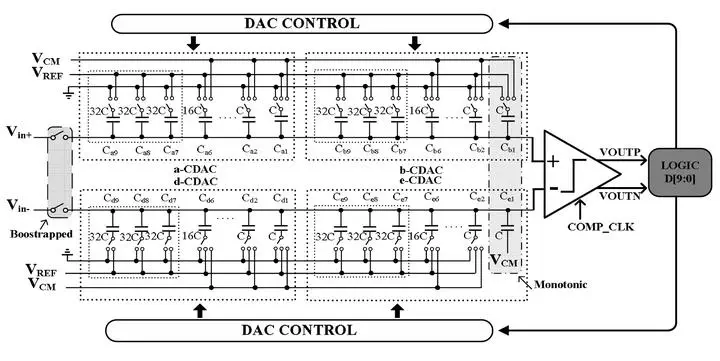

This paper proposes a fully differential 10-bit energy-efficient successive approximation register (SAR) analog-to-digital converter (ADC) that uses bypass window quantization technique based on multiple splits of the most significant bit (MSB) capacitor. Capacitor splitting of the digital-to-analog converter (DAC) is used to set up bypass windows. For signals within the bypass window range, some intermediate quantization are skipped to achieve lower power consumption and higher linearity. The proposed SAR ADC with bypass windows is designed using a standard 180nm CMOS technology. Simulation results show that the average power consumption of the capacitor array is only 72.08 CVREF^2. The differential nonlinearity (DNL) and integral nonlinearity (INL) are within 0.33 LSB and 0.25 LSB, respectively. With 0.6 V supply and 20.83 kHz sampling rate, the effective number of bits (ENOB) of the ADC reaches 9.72 bits, and the figure of merit (FoM) is 2.56 fJ/conv.-step.